# PERFORMANCE MODELS FOR EMBEDDED SOFTWARE PRODUCT LINES

## Dissertation

zur Erlangung des Grades einer

## DOKTORIN DER NATURWISSENSCHAFTEN

der Universität Osnabrück am Fachbereich Mathematik/Informatik/Physik

von

BIRTE KRISTINA FRIESEL

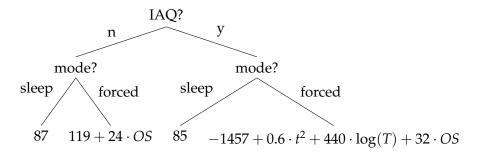

Osnabrück

2024

Tag der mündlichen Prüfung: 17. Februar 2025

Dekan: Prof. Dr. Tim Römer

Gutachter: Prof. Dr.-Ing. Olaf Spinczyk

Prof. Dr.-Ing. Timo Hönig

Software product lines deal with functional properties (features) of configurable software systems. However, these systems also have non-functional properties such as latency, energy usage, or memory footprint. Performance models formalize knowledge about those properties and their relation to individual features; they are often crucial to building competitive products. While the literature offers a variety of performance modeling methods for conventional product lines, these do not address configurable device drivers and hardware components. Moreover, many approaches either rely on time-consuming and error-prone manual annotations, or result in models that are so complex that engineers cannot gain insights by analysing them.

This thesis covers interpretable performance models for configurable embedded systems, including software product lines, configurable hardware components, and hybrid product lines that combine both. It focuses on automation for the entire life cycle, ranging from unattended data acquisition over machine learning methods for model generation to performance-aware product line configuration. In doing so, it shows that the disjoint Product Line Engineering and Internet of Things communities address similar challenges, and combines and extends aspects from both to obtain accurate and interpretable performance models for hybrid and hardware-centric software systems.

Its key contribution is the Regression Model Tree data structure and machine learning method. Regression model trees resemble the structure of feature models, but exclusively rely on benchmark data for model generation. They can be used with software product lines, configurable hardware components and hybrid product lines, and can be learned – and understood – even if no feature model is available. An evaluation on eight product lines and product line-like system components shows that regression model trees are more accurate and less complex than other tree-based modeling methods when applied to hybrid product lines and hardware components.

In addition, this thesis contributes a method for energy measurement automation even if no out-of-band synchronization methods are available, an analysis of whether performance models should be part of feature models or kept separate, a product line perspective on configurable hardware components and device drivers, and case studies that apply regression model trees to real-world product lines. The analysis finds that performance models should be kept separate; regression model trees follow this approach. The case studies cover both manual model analysis and tool-assisted performance-aware configuration of Kconfig-based product lines.

This thesis builds upon decades of prior research and dozens of people who directly and indirectly supported it, and would not be possible without either of those.

First and foremost, I would like to thank my advisor, Prof. Dr.-Ing. Olaf Spinczyk, for giving me the opportunity to pursue this endeavour to begin with and for nudging me into the right direction when needed. Similarly, I am thankful to my parents for supporting me on the long way towards handing in the dissertation.

I am also grateful for the colleagues around the two research groups that I was part of during this journey. This includes (but is certainly not limited to) Hendrik, Ulrich, Horst and Alex of the Embedded System Software group at TU Dortmund, and Marcel of the Embedded Software Systems group at Universität Osnabrück. No matter whether it was research-related or not, you always had a helpful comment at hand. I have fond memories of occasionally getting sore face muscles just from laughing, especially during the 11:30-and-not-a-minute-later Mensa breaks in Dortmund.

Outside of academia, I would like to extend special thanks to Markus, with whom I have had the pleasure of sharing the experience called "life" for the past eleven years — I do not wish to know where I would be without you. I am also very thankful to my close friends, notably Lara, Christian, Nadine, Larissa, and Luzia.

Finally, I would like to acknowledge that occasional random encounters are important and helpful additions to long-standing support from family, friends, and colleagues. This includes people I met – and occasionally even kept in touch with – at conferences, the local hackspace community, and the numerous academia-adjacent entities that I had the joy of interacting with online.

Parts of the contributions presented in this thesis have been published in the following peer-reviewed conference and workshop proceedings.

- 1. Birte Friesel, Markus Buschhoff, and Olaf Spinczyk. "Annotations in Operating Systems with Custom AspectC++ Attributes". In: *Proceedings of the 9th Workshop on Programming Languages and Operating Systems*. PLOS '17. Shanghai, China: Association for Computing Machinery, Oct. 2017, pp. 36–42. ISBN: 978-1-4503-5153-9. DOI: 10.1145/3144555.3144561 [FBS17]

- 2. Birte Friesel, Markus Buschhoff, and Olaf Spinczyk. "Parameter-Aware Energy Models for Embedded-System Peripherals". In: *Proceedings of the 13th International Symposium on Industrial Embedded Systems*. SIES '18. Graz, Austria: IEEE, June 2018. DOI: 10.1109/SIES.2018.8442096 [FBS18]

- 3. Birte Friesel and Olaf Spinczyk. "Poster Abstract: I<sup>2</sup>C Considered Wasteful: Saving Energy with Host-Controlled Pull-Up Resistors". In: *Proceedings of the 18th International Conference on Information Processing in Sensor Networks.* IPSN '19. Montreal, QC, Canada: Association for Computing Machinery, Apr. 2019, pp. 315–316. ISBN: 978-1-4503-6284-9. DOI: 10.1145/3302506. 3312606 [FS19]

- 4. Birte Friesel, Lennart Kaiser, and Olaf Spinczyk. "Automatic Energy Model Generation with MSP430 EnergyTrace". In: *Proceedings of the Workshop on Benchmarking Cyber-Physical Systems and Internet of Things*. CPS-IoTBench '21. Nashville, TN, USA: Association for Computing Machinery, May 2021, pp. 26–31. ISBN: 978-1-4503-8439-1. DOI: 10.1145/3458473.3458822 [FKS21]

- 5. Birte Friesel and Olaf Spinczyk. "Data Serialization Formats for the Internet of Things". In: *Electronic Communications of the EASST* 80 (Sept. 2021). DOI: 10.14279/tuj.eceasst.80.1134 [FS21]

- 6. Birte Friesel and Olaf Spinczyk. "Performance is not Boolean: Supporting Scalar Configuration Variables in NFP Models". In: *Tagungsband des FG-BS Frühjahrstreffens* 2022. Hamburg, Germany: Gesellschaft für Informatik e.V., Mar. 2022. DOI: 10.18420/fgbs2022f-03 [FS22b]

- 7. Birte Friesel and Olaf Spinczyk. "Regression Model Trees: Compact Energy Models for Complex IoT Devices". In: *Proceedings of*

the Workshop on Benchmarking Cyber-Physical Systems and Internet of Things. CPS-IoTBench '22. Milan, Italy: IEEE, May 2022, pp. 1–6. DOI: 10.1109/CPS-IoTBench56135.2022.00007 [FS22c]

- 8. Birte Friesel and Olaf Spinczyk. "Black-Box Models for Non-Functional Properties of AI Software Systems". In: *Proceedings of the 1st International Conference on AI Engineering: Software Engineering for AI*. CAIN '22. Pittsburgh, PA, USA: Association for Computing Machinery, May 2022, pp. 170–180. ISBN: 978-1-4503-9275-4. DOI: 10.1145/3522664.3528602 [FS22a]

- 9. Birte Friesel et al. "On the Relation of Variability Modeling Languages and Non-Functional Properties". In: *Proceedings of the 26th International Systems and Software Product Line Conference Volume B.* SPLC '22. Graz, Austria: Association for Computing Machinery, Sept. 2022, pp. 140–144. ISBN: 978-1-4503-9206-8. DOI: 10.1145/3503229.3547055 [Fri<sup>+</sup>22b]

- 10. Birte Friesel et al. "kconfig-webconf: Retrofitting Performance Models onto Kconfig-Based Software Product Lines". In: *Proceedings of the 26th International Systems and Software Product Line Conference Volume B. SPLC '22. Graz, Austria: Association for Computing Machinery, Sept. 2022, pp. 58–61. ISBN: 978-1-4503-9206-8. DOI: 10.1145/3503229.3547026 [Fri+22a]*

- Birte Friesel, Marcel Lütke Dreimann, and Olaf Spinczyk. "A Full-System Perspective on UPMEM Performance". In: *Proceedings of the 1st Workshop on Disruptive Memory Systems*. DIMES '23. Koblenz, Germany: Association for Computing Machinery, Oct. 2023, pp. 1–7. ISBN: 979-8-4007-0300-3. DOI: 10.1145/3609308. 3625266 [FLS23]

I have extended and re-evaluated some of the corresponding algorithms since then. Hence, the evaluation data sets and results presented in this thesis are not necessarily identical with the ones presented in the publications listed above.

The tools, algorithms, and observations presented in this thesis have also contributed to the following peer-reviewed publications.

- Robert Falkenberg et al. "PhyNetLab: An IoT-Based Warehouse Testbed". In: Proceedings of the Federated Conference on Computer Science and Information Systems. FedCSIS '17. Prague, Czech Republic: IEEE, Sept. 2017, pp. 1051–1055. DOI: 10.15439/2017F267 [Fal+17]

- 2. Markus Buschhoff, Birte Friesel, and Olaf Spinczyk. "Energy Models in the Loop". In: *Procedia Computer Science* 130 (2018). Proceedings of the 9th International Conference on Ambient

- Systems, Networks and Technologies (ANT 2018) / the 8th International Conference on Sustainable Energy Information Technology (SEIT 2018) / Affiliated Workshops, pp. 1063–1068. ISSN: 1877-0509. DOI: 10.1016/j.procs.2018.04.154 [BFS18]

- 3. Marcel Lütke Dreimann, Birte Friesel, and Olaf Spinczyk. "Het-Sim: A Simulator for Task-based Scheduling on Heterogeneous Hardware". In: *Companion of the 15th ACM/SPEC International Conference on Performance Engineering*. ICPE '24 Companion. London, UK: Association for Computing Machinery, May 2024, pp. 261–268. ISBN: 979-8-4007-0445-1. DOI: 10.1145/3629527. 3652275 [LFS24]

Finally, I have supervised the following Bachelor's theses over the course of my research.

- 1. Leon Nienhüser. "Bewertung der Energieeffizienz FRAM-basierter Zustandssicherungsverfahren". Feb. 2020.

- 2. Kevin Lass. "Automatische Zustandssicherung und -wiederherstellung für Gerätetreiber". Aug. 2020.

- 3. Janis Falkenhagen. "Verfeinerung parametrisierter Energiemodelle mithilfe von Changepoint Detection". Sept. 2020.

- 4. Lennart Kaiser. "Automatisierte Energiemodellerstellung mit MSP430 EnergyTrace". Sept. 2020.

- 5. Tom Brüning. "Entwicklung eines AR-basierten Demonstrators für KI in ressourcenbeschränkten eingebetteten Systemen". Sept. 2023.

- 6. Johannes Horas. "Generierung von ressourcenoptimierten Entscheidungsbäumen für eingebettete Systeme". May 2024.

# CONTENTS

| 1 | Intro        | oduction 1                                           |  |  |  |  |

|---|--------------|------------------------------------------------------|--|--|--|--|

|   | 1.1          | Challenges 2                                         |  |  |  |  |

|   |              | Goals 4                                              |  |  |  |  |

|   | 1.3          | Contributions 5                                      |  |  |  |  |

|   | 1.4          | Structure 6                                          |  |  |  |  |

| 2 |              | ware Product Lines 9                                 |  |  |  |  |

|   |              | Feature Models 10                                    |  |  |  |  |

|   |              | Performance Models 13                                |  |  |  |  |

|   |              | Variability Modeling Languages 15                    |  |  |  |  |

|   |              | The Kconfig Language 18                              |  |  |  |  |

|   | -            | Machine Learning 20                                  |  |  |  |  |

|   |              | 2.5.1 Least-Squares Regression 22                    |  |  |  |  |

|   |              | 2.5.2 Regression Trees 26                            |  |  |  |  |

|   |              | 2.5.3 Lookup Tables 36                               |  |  |  |  |

|   | 2.6          |                                                      |  |  |  |  |

|   |              | 2.6.1 Prediction Error 38                            |  |  |  |  |

|   |              | 2.6.2 Complexity 42                                  |  |  |  |  |

|   | 2.7          | Evaluation Targets 43                                |  |  |  |  |

|   | 7            | 2.7.1 Compile-Time Variability 44                    |  |  |  |  |

|   |              | 2.7.2 Run-Time Variability 45                        |  |  |  |  |

|   | 2.8          | Chapter Summary 47                                   |  |  |  |  |

| 3 |              | gy Models 49                                         |  |  |  |  |

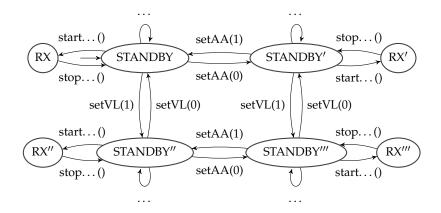

| J | 3.1          | State Machines 50                                    |  |  |  |  |

|   | _            | Related Work 52                                      |  |  |  |  |

|   | <i>J</i>     | 3.2.1 Modeling Methods 52                            |  |  |  |  |

|   |              | 3.2.2 Model Attributes 53                            |  |  |  |  |

|   | 3.3          | Parameterized Priced Timed Automata 54               |  |  |  |  |

|   |              | Benchmark Generation 57                              |  |  |  |  |

|   |              | 3.5 Model Learning 58                                |  |  |  |  |

|   | 55           | 3.5.1 Identification of Relevant Features 59         |  |  |  |  |

|   |              | 3.5.2 Unsupervised Least-Squares Regression 60       |  |  |  |  |

|   |              | 3.5.3 Example 62                                     |  |  |  |  |

|   | 3.6          | Evaluation Targets 63                                |  |  |  |  |

|   | 9            | 3.6.1 MIMOSA 64                                      |  |  |  |  |

|   |              | 3.6.2 BME680 Environmental Sensor 65                 |  |  |  |  |

|   |              | 3.6.3 CC1200 Radio Transceiver 68                    |  |  |  |  |

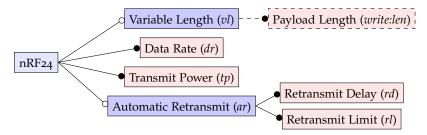

|   |              | 3.6.4 nRF24 Radio Transceiver 69                     |  |  |  |  |

|   | 3.7          |                                                      |  |  |  |  |

| 4 |              | lem Statement 73                                     |  |  |  |  |

| 5 |              | Acquisition 77                                       |  |  |  |  |

| J | 5.1          | Benchmarking Koonfig-Based Software Product Lines 77 |  |  |  |  |

|   | <i>J</i> ••• | 5.1.1 User-Provided Commands 78                      |  |  |  |  |

|   |              | J = = = = = = = = = = = = = = = = = = =              |  |  |  |  |

|   |      | 5.1.2 Sampling 78                            |

|---|------|----------------------------------------------|

|   | 5.2  | Energy Benchmark Synchronization 79          |

|   |      | 5.2.1 EnergyTrace 80                         |

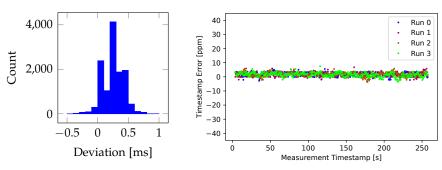

|   |      | 5.2.2 Baseline Evaluation 83                 |

|   |      | 5.2.3 Benchmark Synchronization 87           |

|   |      | 5.2.4 Timing Accuracy 89                     |

|   |      | 5.2.5 Drift Compensation 91                  |

|   |      | 5.2.6 Related Work 96                        |

|   | 5.3  | Chapter Summary 97                           |

| 6 | Vari | ability Models 99                            |

|   | 6.1  |                                              |

|   |      | 6.1.1 Qualitative Analysis 102               |

|   |      | 6.1.2 Quantitative Analysis 105              |

|   | 6.2  | Run-Time Features in Peripherals 108         |

|   | 6.3  |                                              |

|   |      | 6.3.1 Relevance 112                          |

|   |      | 6.3.2 Prediction 113                         |

|   | 6.4  | Boolean Features in Peripherals 114          |

|   |      | 6.4.1 Relevance 116                          |

|   |      | 6.4.2 Prediction 116                         |

|   | 6.5  | Chapter Summary 117                          |

| 7 | Reg  | ression Model Trees 119                      |

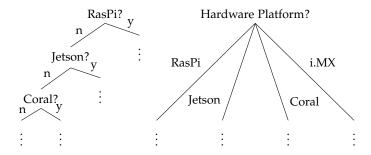

|   | 7.1  | Non-Binary Regression Trees 119              |

|   |      | 7.1.1 Data Structure 120                     |

|   |      | 7.1.2 Algorithms 121                         |

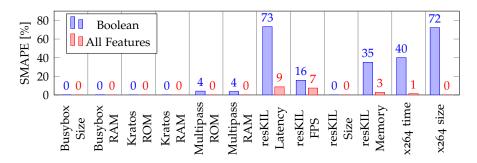

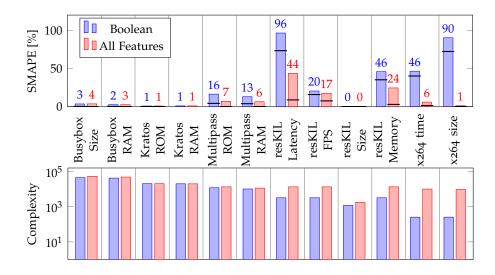

|   |      | 7.1.3 Evaluation 123                         |

|   |      | Numeric Features in Leaf Nodes 125           |

|   | 7.3  | Data Structure 128                           |

|   | 7.4  | Machine Learning Algorithm 130               |

|   |      | 7.4.1 Co-Dependent Feature Detection 130     |

|   |      | 7.4.2 Tree Generation 132                    |

|   |      | 7.4.3 Queries 134                            |

|   | 7.5  | Evaluation 134                               |

|   |      | 7.5.1 Setup 135                              |

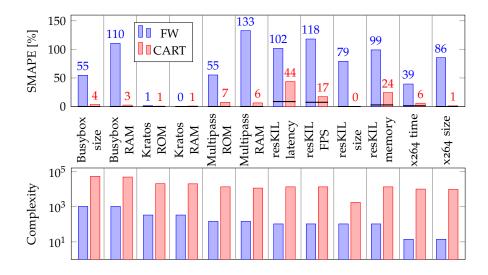

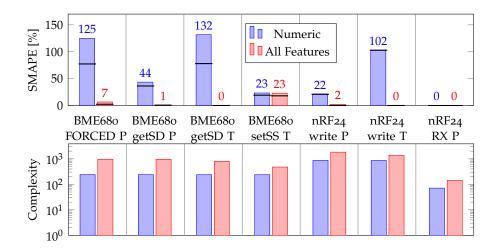

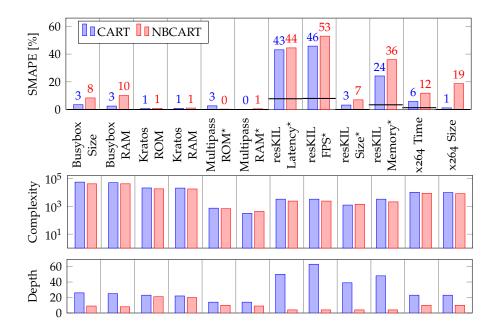

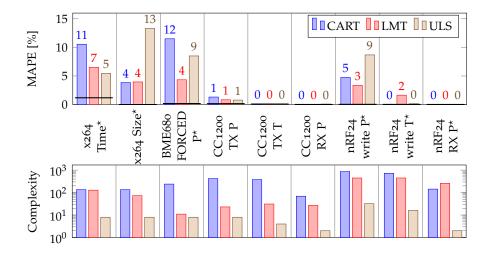

|   |      | 7.5.2 Accuracy and Interpretability 137      |

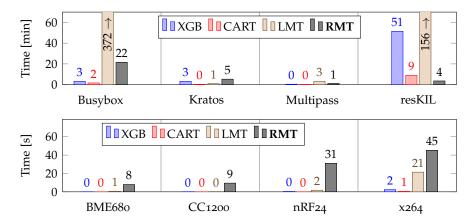

|   |      | 7.5.3 Learning Time 141                      |

|   | 7.6  | ·                                            |

|   |      | 7.6.1 Modeling Methods 143                   |

|   |      | 7.6.2 Sampling 144                           |

|   |      | Chapter Summary 145                          |

| 8 | 1 1  | lications 147                                |

|   | 8.1  | Black-Box Models for AI Software Systems 148 |

|   |      | 8.1.1 Introduction 149                       |

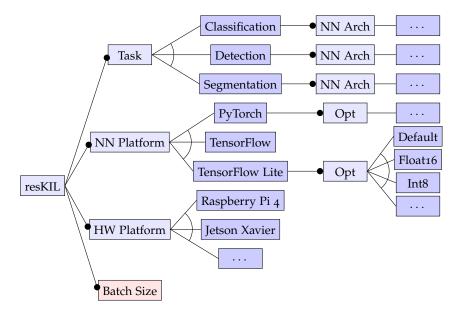

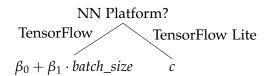

|   |      | 8.1.2 The resKIL Product Line 150            |

|   |      | 8.1.3 Benchmark Setup 153                    |

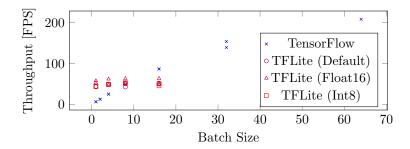

|   |      | 8.1.4 Findings 154                           |

```

8.1.5

Related Work

8.1.6

Conclusion

160

8.2 Performance-Aware Product Line Configuration

160

8.2.1

Concept

162

8.2.2

Implementation

163

8.2.3

Workflow

166

Case Studies

8.2.4

167

8.2.5

Related Work

170

8.2.6

Conclusion

171

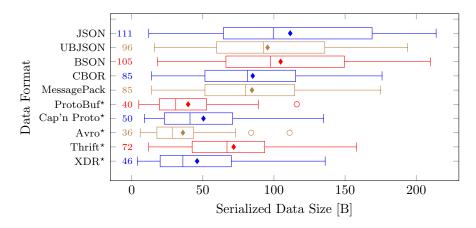

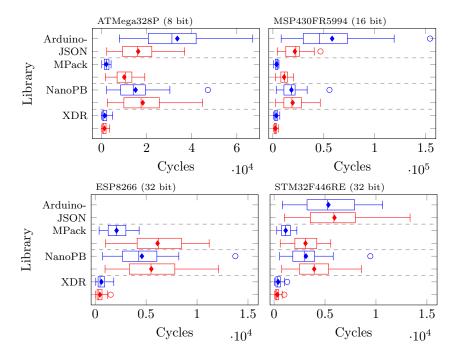

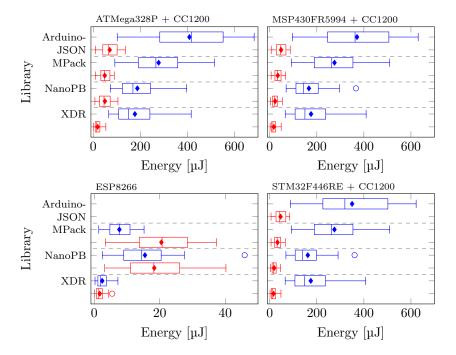

8.3 Data Serialization Formats for the Internet of Things

8.3.1

Hardware Platforms

173

8.3.2

Data Formats

Implementations

8.3.3

177

Related Work

8.3.4

178

8.3.5

Behaviour Models

180

8.3.6

Observations

182

8.3.7

Conclusion

186

8.4 Chapter Summary

187

9 Conclusion

189

9.1 Summary

189

9.2 Contributions

191

9.3 Limitations and Future Work

195

9.3.1

Data Acquisition

Regression Model Trees

9.3.2

196

Applications

198

9.3.3

9.4 Final Remarks

198

Bibliography

199

List of Figures

219

List of Tables

223

Acronyms

```

INTRODUCTION

From an outside perspective, building an embedded system may seem trivial. After all, there is a wide range of commercially available offers for hardware components as well as a variety of commercial and open-source software components to choose from. Hardware components include processors, sensors, actuators, and communication interfaces; software components include operating systems, user-space applications, and data serialization formats and libraries.

Consider a wireless sensor node that regularly performs air quality measurements and wirelessly transmits them to a central hub. One might assume that the system designer simply needs to combine a suitable air quality sensor, microcontroller, and radio chip with an operating system, a radio protocol, and some configuration and glue code. Once they have verified that the result fulfils the *functional requirements* (i.e., it successfully measures and transmits air quality data), they can deploy it or start selling it.

Of course, in practice, it is not so easy. A battery-powered environmental sensor installed in a remote location defeats its purpose if it only works for a few days before the battery is empty, and an operating system kernel is useless if it takes up so much memory that user-space applications frequently encounter out-of-memory errors. Hence, in order to build a useful product, developers need to take *non-functional requirements* such as battery runtime or memory usage into account [Glio7]. These depend on the *non-functional properties* (or *performance attributes*) of each system component, which in turn depend on the configuration and combination of system components: a compute-intensive algorithm on an energy-efficient CPU or a light-weight algorithm on a less efficient CPU may be fine, while an inefficient algorithm on an inefficient CPU is not.

This thesis takes a deeper look into the what, why, and how of performance attributes and performance models for embedded system components. Specifically, it looks into ways of predicting how a component's configuration affects its performance attributes, and how performance models and *product lines* interact. At this point, we can think of product lines as configurable software or hardware components – I will provide a detailed definition, and an explanation as to why this simplification is not quite correct, in Chapter 2. Before that, let us look into challenges that embedded developers face when dealing with non-functional requirements, corresponding research questions, and the resulting contributions to the state of the art.

#### 1.1 CHALLENGES

The importance of performance attributes and non-functional requirements stems from the variety of resource constraints faced by embedded systems. Available energy, ROM and RAM space, and processing power are typically limited and should be used responsibly to minimize hardware cost and maximise operating time. However, functional requirements and system properties do not account for this – they only describe aspects such as environmental attributes supported by a certain sensor, or operating system APIs exposed to user-space applications.

Performance attributes¹ describe the energy usage of hardware components, memory usage of software components, and similar. They do not explain what a component does, but how efficient, expensive, or similar it is. For instance, if two algorithms A and B have identical functional attributes, but A only needs half as much processing time, choosing A over B may allow the system designer to use a less powerful, and thus cheaper, microcontroller. Similarly, if a radio chip supports a low-power sleep mode, using this sleep mode may require less power than keeping it idle all the time. However, as starting a transmission from sleep mode typically takes more time than doing so from idle mode, the expected usage scenario determines whether using sleep mode really is more efficient.

Non-functional requirements may state, for instance, that a certain product must have a minimum battery runtime of four weeks under certain usage conditions. In order to reason about them, system designers need to know the non-functional properties of each system component. This is not a trivial task: many software and hardware components resemble product lines that offer a variety of configuration options, all of which can influence their non-functional properties in often unexpected and undocumented manners [Ach<sup>+</sup>22]. So, there is not just a choice between different hardware or software components, but also between different configurations of the same component.

In theory, system designers could run benchmarks for each different combination and configuration of system components that fulfils the specified functional requirements, and then determine the optimal setup for their non-functional requirements. In practice, this is not feasible, as n boolean configuration options result in up to  $2^n$  different configurations, and software projects like busybox or the Linux kernel expose thousands of options.

*Performance models* reduce the need for benchmarks by predicting non-functional properties of arbitrary system configurations. If system designers have such a tool at their disposal, they can obtain estimates for performance attributes of individual system components. This

<sup>1</sup> Performance attributes appear under a variety of names; common synonyms in the literature include non-functional properties and extra-functional properties [DZT12].

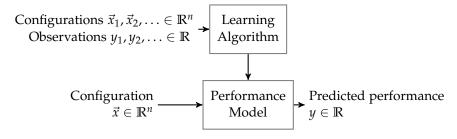

Figure 1.1: Relation between learning algorithms and performance models.

allows them to reason about the effect of toggling individual configuration options before a prototype has been built, or to devise performance-aware run-time algorithms [SSS10; HK17; Her<sup>+</sup>21]. As all models come with a certain level of uncertainty, benchmarks are still relevant for verification of model predictions, e.g. before committing on a configuration for manufacturing [Hur<sup>+</sup>11]. However, time-consuming benchmark campaigns that cover all valid system configurations are no longer necessary.

Ideally, a performance model is both accurate enough to generate useful predictions and simple enough to be understandable by humans, thus allowing them to reason about the effect of individual configuration options by looking at the model rather than by comparing predictions for dozens of pairs of configurations. Otherwise, users should at least have helpful tooling that annotates the performance effect of configuration options. At the same time, performance models do not appear out of thin air, and generating or updating them is at least as important as knowing how to use them [Har<sup>+</sup>16]. Machine learning algorithms help with this, but may rely on manually specified model templates or come up with complex models that are beyond human understanding.

Fig. 1.1 illustrates the relation between benchmarks, machine learning algorithm, and the resulting performance model. First, domain engineers perform a series of benchmarks that cover a range of system configurations  $\vec{x}_i$  and obtain corresponding performance observations  $y_i$  (e.g. latency or power). Next, they pass configurations and observations to a machine learning algorithm that learns to predict performance y from configuration  $\vec{x}$ . Embedded developers can then use the resulting performance model to predict the performance of individual system configurations, simulate how changing configuration options would affect performance, and – if the model is understandable – gain further insights into system behaviour. Crucially, at this stage, they do not need access to raw observations or a test bench setup.

These challenges and goals finally bring us to the title of this thesis: performance models for embedded software product lines. I have spent the past years examining this topic from several angles, ranging from automated energy measurements over machine learning algorithms for performance model generation to tools for performance-aware

product line configuration. This document serves as a collection of my findings and scientific contributions towards the aforementioned goals. It combines extended and updated versions of peer-reviewed papers that I authored over the course of my PhD studies with a common background, motivation, and set of evaluation targets.

#### 1.2 GOALS

The concept of performance models for configurable hardware and software components is far from being a new idea. It has been around for at least two decades, and two different scientific communities have been examining it closely.

On the one hand, the Cyber-Physical Systems and Internet of Things (CPS and IoT) community uses *energy models* to predict the energy requirements and timing behaviour of embedded systems and individual hardware components. The focus lies on hardware states (e.g. transmit, receive, and idle modes of a radio chip), transitions between them, and their timing and energy attributes. A key component of energy model generation is benchmark automation, as manual energy measurements are tedious and error-prone [ZO13]. Running energy benchmarks also requires suitable measurement equipment, and a benchmark application that exercises all hardware states and transitions.

On the other hand, the Software Product Line Engineering (SPLE) community uses *non-functional property models* to predict non-functional attributes of software product lines. Here, the focus lies on *variability models* that help manage the design space by organizing individual configuration options in a tree hierarchy and specifying cardinalities and dependencies. Another important aspect is handling the hundreds or even tens of thousands of configuration options that prohibit an exhaustive state space exploration and hinder reasoning about the importance of individual options. Instead, benchmarks first need to decide on a sampling strategy, and models must be able to predict non-functional attributes of previously unseen configurations.

Both communities have a variety of additional names for energy models and non-functional property models. These include resource models, power models, quality models, performance-influence models, and performance prediction models [VSo8; McC<sup>+</sup>11; Sie<sup>+</sup>12b; Sie<sup>+</sup>15; Guo<sup>+</sup>18]. In this thesis, I use the umbrella term *performance models* to cover all of them.

As far as I am aware, there is little overlap or cooperation between CPS/IoT and SPLE researchers. While there are indeed differences in the challenges they face and priorities they set, I do not consider them to be prohibitive, and in fact think that both communities can benefit from each other. Hence, this thesis stands at the intersection of Energy Modeling and Product Line Engineering research. It covers

performance models for hardware and software components, and also examines hybrid product lines whose variability entails both hardware and software configuration options.

More specifically, my goal is to make performance models more accessible to the general public by minimizing the amount of specialized equipment, knowledge, and manual labour required for data acquisition, performance model generation, and performance model usage. All methods should be applicable to performance models for software product lines, energy models for embedded devices, and hybrid product lines that encompass both. At the same time, I want the automatically generated models to provide insights into system behaviour rather than just behaving as black boxes. Again, gaining these insights should not require an extensive skill set: performance models should be simple enough to be understandable just from looking at them, and performance-aware configuration software should be intuitive.

#### 1.3 CONTRIBUTIONS

On the way towards unattended data acquisition, this thesis contributes the *dfatool* benchmark and model generation framework that supports both Kconfig-based software product lines and energy measurements of embedded peripherals. The latter requires a method for synchronizing benchmark events to energy measurements in order for its automation to work. However, the *out-of-band signals* that conventional synchronization methods rely on may not be available e.g. due to hardware not exposing suitable outputs or due to lack of funding for measurement equipment with appropriate inputs.

This challenge leads to research question **RQ1**: are automated and accurate CPS/IoT energy measurements feasible on hardware that lacks suitable out-of-band synchronization methods? As part of the answer, I will present a generic *drift compensation* algorithm that exclusively relies on on-board timers and in-band signalling, and show how it allows for automated energy measurements on \$20 commercial off-the-shelf hardware.

When it comes to performance model generation, the first question is how variability model and performance model should relate. Hence, **RQ2** is: should performance models be integrated into variability models, or should they be separate entities? This is a fundamental question, as it dictates requirements for performance model structure and machine learning methods.

In a similar vein, the differences and similarities between nonfunctional property models and energy models beg the question whether it is viable to devise a common machine learning algorithm for both domains. I.e., **RQ3**: can a common machine learning algorithm for SPLE and CPS/IoT performance models provide lower prediction

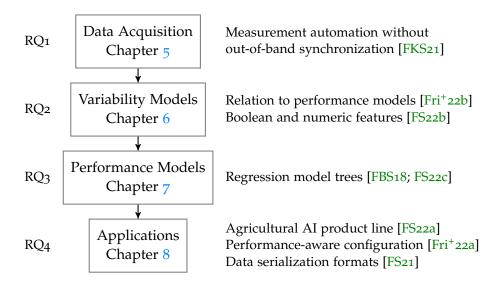

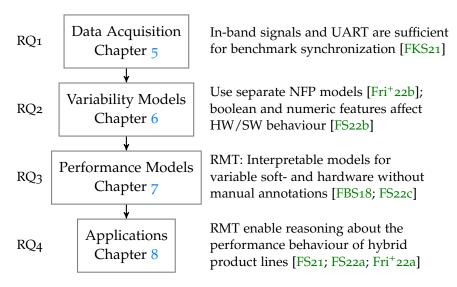

Figure 1.2: Research questions addressed in this thesis as well as contributions and corresponding publications in relation to a typical performance model generation and usage workflow.

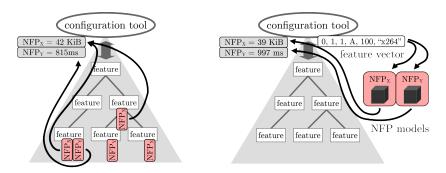

error and model complexity than conventional approaches, without requiring manually provided domain information or model structure? Here, my key contribution is the novel *regression model tree* machine learning algorithm and performance model data structure.

Finally, model usage covers practical considerations. These include performance trade-offs in an artificial intelligence (AI) application and in data serialization format selection for wireless sensor networks. The AI application deviates from typical approaches in the literature by using an SPL-inspired black-box approach rather than the white-box variant that is common in the AI domain. This warrants an additional question (**RQ4**): are product line engineering and performance modeling techniques also applicable to product lines that cover soft- and hardware variability? In addition, I contribute a utility for performance-aware configuration of Kconfig-based product lines.

Fig. 1.2 gives an overview of the research questions, contributions, and publications covered in this thesis. It follows the typical workflow of performance model generation for an existing product line, starting out with data acquisition. Once all benchmark data is available, a machine learning algorithm (such as regression model trees) can build a performance model, and users can apply it to real-world engineering and optimization tasks.

#### 1.4 STRUCTURE

The next two chapters cover software product lines and performance models for software product lines (Chapter 2) as well as energy models for hardware peripherals (Chapter 3). This includes an introduction

to variability models, related work on performance models and machine learning algorithms, quality metrics that will be used for model evaluation, and other definitions that are relevant throughout the entire document. They also introduce the product lines and hardware components that serve as application examples and evaluation targets throughout this thesis. Chapter 4 provides the problem statement: a re-cap of the research questions and how they relate to the state of the art presented in the introduction chapters. The following four chapters answer RQ1 through RQ4 and present additional contributions.

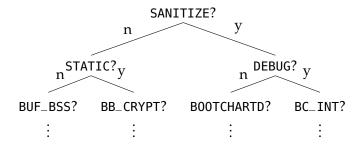

First, Chapter 5 covers benchmark generation and data acquisition. For software product lines, this boils down to an implementation of existing data acquisition methods. For embedded peripherals, automation is not always so easy – here, I will present my answer to RQ1. Next, Chapter 6 examines the relation between variability models and performance models, and what kind of configuration options (boolean or numeric) a performance model should consider for performance prediction. Based upon these findings, Chapter 7 motivates, defines, and evaluates the regression model tree data structure and machine learning algorithm. Chapter 8 contains further applications of performance models to practical issues such as data serialization format selection in wireless sensor networks and performance optimization of an agricultural AI product line. Finally, chapter 9 concludes and gives an outlook into future research avenues.

To introduce the concepts of software product lines and performance models, let us consider the case of an experienced embedded engineer who wants to design a minimal embedded *Operating System* (OS) to support the evaluation of hardware and software components for *Internet of Things* (IoT) devices. It must support several target architectures, provide device drivers for common peripheral interfaces, and should be limited to the bare necessities apart from that. Since the target architecture dictates which compiler and low-level implementations (e.g. context switch code or on-board peripheral drivers) must be used to obtain a binary image that can be executed on it, the engineer cannot compile a single OS image that works on any architecture. However, maintaining an individual operating system code base for each target architecture is not desirable either.

Thanks to their domain knowledge, the engineer knows that an operating system contains numerous architecture-agnostic components that do not need to be adapted for different target architectures. In this case, architecture-specific low-level modules are the only variable components within the operating system. If the engineer ensures that architecture-specific components are only linked into the operating system image when needed, and defines a common programming interface for accessing them, they can compile binaries for any supported architecture by selectively including / excluding components during compilation. This reasoning about features, components, and interfaces between them is called domain engineering. The resulting operating system is not a complete and ready-to-use product by itself, but rather a Software Product Line (SPL) that can be compiled into several different products depending on the selected features [Sin+07; Keh<sup>+</sup>21]. In this example, each target architecture is a feature, so there is one operating system product per target architecture.

Now, assume that a developer wants to use this operating system to run a signal processing application. The application is simple enough to run on any supported target architecture – hence, all products have the same *functional* properties. However, hardware cost, energy usage, latency, and throughput can vary. Some platforms may have low cost, but high latency and energy requirements, while more expensive hardware may offer improved throughput or energy efficiency. In general, there is no single best product; instead, each developer must choose according to their optimization goals and design constraints. As such, these *performance attributes* – also known as *Non-Functional*

*Properties* (NFPs) – play a vital role in the configuration of software product lines for embedded platforms.

While configuring an optimal product may be easy for this toy example, it is much less so in real-world product lines with hundreds or even thousands of features. Here, *models* that predict how individual features affect the non-functional properties of individual products come into play. They can be used to predict the effect of features at configuration time, and to automatically configure features that are not relevant for functional product properties [Ola<sup>+</sup>12; SSS10]. Preferably, these models should be accurate, easy to understand, and require a minimal amount of manual intervention during training.

This chapter gives an overview of methods and definitions for each of these aspects:

- feature models for software product lines,

- performance models for non-functional product properties,

- variability modeling languages that express feature models as text, with a special focus on the Kconfig language,

- machine learning methods for performance model generation, and

- quality metrics that assess model accuracy and interpretability.

The operating system product line introduced in the previous paragraphs will serve as a running example throughout the chapter. At the end, I will present the real-world software product lines that serve as evaluation targets in this thesis.

#### 2.1 FEATURE MODELS

As the introductory example shows, product lines must be configured into concrete products before they can be used. With an appropriate configuration interface, this is easy to achieve – it can be as simple as using conditional blocks in Makefiles and source code, and setting compile-time variables and pre-processor flags to indicate the target architecture. For instance, a user could run make arch=msp430 to compile an operating system product for the MSP430 architecture. This, in turn, would pass the -DARCH\_MSP430 flag to the compiler, causing it to include architecture-specific code that is guarded by #ifdef ARCH\_MSP430 statements and leave out code that is specific to other architectures.

When dealing with real-world software product lines, such as the busybox multi-call binary<sup>1</sup> or the Linux kernel, such a simple approach

<sup>1</sup> In busybox documentation, the term *multi-call binary* describes a single binary that provides distinct applets depending on how it is called. For instance, busybox ls behaves like the ls utility, and busybox telnet provides a telnet client. Users define the set of supported applets at compile time.

is no longer sufficient. These expose thousands of features with complex dependencies, allowing them to be used in – and optimized for – a wide range of use cases. Manual feature and dependency management is not feasible at this scale. Instead, they use a formal *feature model* that defines and structures the features within the SPL, where each *feature* is a product characteristic such as support for specific architectures or device drivers [Kan<sup>+</sup>90]. Combined with a configuration frontend that can read the feature model and save individual configurations, this allows users to define and build valid configurations [Ape<sup>+</sup>13].

A feature model breaks down a product line's variability into a hierarchy of features [Kan<sup>+</sup>90]. *Abstract* features group sub-features but do not provide any product characteristic by themselves, whereas *concrete* features can be enabled or disabled and affect the resulting product. Individual features are either *mandatory* (they must be enabled if the parent is enabled) or *optional* (they can be enabled if the parent is enabled). In both cases, a sub-feature cannot be enabled if the parent feature is disabled. Each group of sub-features has one of three relations:

- and: each mandatory feature must be selected (this is the default);

- alternative (exclusive or): exactly one feature must be selected;

- *or* (inclusive or): at least one feature must be selected.

Product line engineers can also specify more complex cardinalities, such as the minimum and maximum number of enabled sub-features. By default, concrete features are boolean, i.e., they can be disabled or enabled. Users may also specify *numeric* features that take a number from the domain  $\mathbb N$  or  $\mathbb R$  (depending on application), and *string* features that take arbitrary user-provided data (e.g. interface names).

A feature model can be limited to functional product characteristics, or include implementation details such as different algorithms that achieve the same function from an end-user perspective, but have different non-functional properties [CHEo5]. The latter allows stakeholders to compare and optimize performance attributes of configurations that fulfil the same functional requirements. Product line engineers may also design a hierarchy of feature models to separate functional aspects and implementation details [Ros+11]. Feature models in this thesis contain both kinds of features – however, the findings also apply to disaggregated models.

When using a feature model to configure an SPL, each product is defined by a unique configuration of concrete features, or in formal terms: a *feature vector* that maps each feature to a value [Nai $^+$ 2o]. In the simplest case, where features can only be disabled or enabled, products of a product line with n features can be unambiguously described with feature vectors from the set  $\{0,1\}^n$ . In general, the domain may also include numeric and string entries, but the concept of a feature vector remains the same.

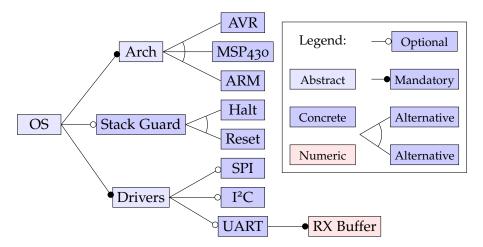

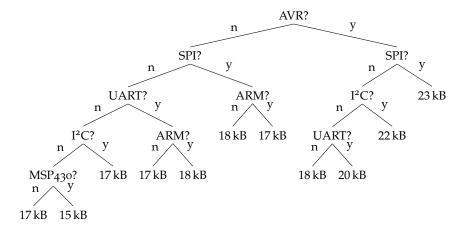

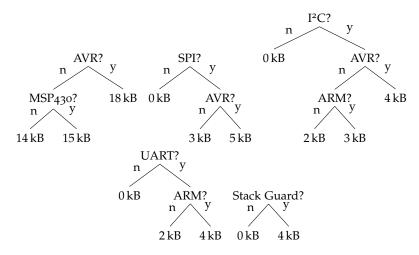

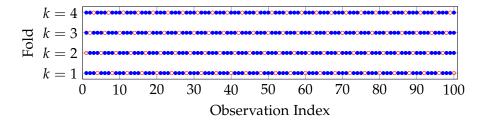

Figure 2.1: Feature model for a sample operating system product line.

Fig. 2.1 shows the feature model of the OS product line that serves as running example in this chapter, using the established visualization method [Kan<sup>+</sup>90]. The OS root feature is abstract, so it cannot be enabled or disabled individually. It defines that an operating system product consists of the architecture it is compiled for, peripheral interface drivers, and an optional stack guard feature. Architecture and drivers are abstract as well.

As each product only supports a single architecture, and compiling an operating system without underlying hardware is not sensible in this case, the mandatory *Arch* feature indicates that exactly one of its sub-features must be selected: AVR, MSP430, or ARM. These serve as short placeholders for specific microcontroller types, such as AVR ATMega2560 or MSP430FR5994.

The optional *Stack Guard* feature uses canary values to detect stack overflows. If enabled, it can either halt the operating system once it has detected a stack overflow or trigger a hardware reset; hence, *Halt* and *Reset* are alternative features. Due to the implicit dependency relation imposed by the tree structure, Halt and Reset can only be enabled if Stack Guard is enabled.

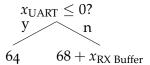

The *SPI*, *I*<sup>2</sup>C and *UART* drivers can be enabled and disabled individually. SPI and I<sup>2</sup>C use application-provided buffers, whereas the UART driver provides an OS-managed buffer for incoming transmissions. Therefore, if the UART driver is enabled, users must configure RX buffer size.

Product line engineers can extend the feature model with explicit dependencies, also known as cross-tree constraints. For example, an engineer may limit RX buffer size depending on the selected architecture to ensure that sufficient RAM is available for other tasks: RX Buffer  $\leq 256 \land (\text{AVR} \Rightarrow \text{RX Buffer} \leq 64)$ . Or, due to limited processing resources, they may specify that Stack Guard is not available on ATMega: ATMega  $\Rightarrow \neg$ Stack Guard.

These constraints ensure that any valid configuration results in a working product. The feature vector encodes configurations as follows.

$$\vec{x} = (x_{\text{AVR}}, x_{\text{MSP430}}, x_{\text{ARM}}, x_{\text{Stack Guard}}, x_{\text{Halt}}, x_{\text{Reset}}, x_{\text{SPI}}, x_{\text{I}^2\text{C}}, x_{\text{UART}}, x_{\text{RX Buffer}}) \in \{0, 1\}^9 \times \mathbb{N}^1$$

However, there is no description of non-functional product attributes, and thus users without domain knowledge cannot aim for low cost or resource usage when configuring products. Performance models address just that.

#### 2.2 PERFORMANCE MODELS

Mathematically speaking, a *performance model* (or *NFP model*) is a function  $f: \vec{x} \mapsto y$  that predicts a performance attribute (non-functional property, NFP) y of a product line configuration  $\vec{x}$ . For instance, it may predict the size of a kernel image or busybox binary from a .config file, the throughput of a video encoder from its command-line configuration, the latency of a neural network from its layout, or operating system size from the feature vector shown above.

For the operating system example, assume that the developer is interested in hardware cost (€) and binary size (kB). The former is relevant for the sales department, and the latter dictates how much space is available for applications and whether the operating system product fits onto its target platform in the first place.

Performance models can be designed and interpreted manually by a domain expert, generated automatically by a machine learning algorithm and interpreted by performance-aware configuration software, or built and used with a combination of both. This section only covers manual specification and interpretation using feature- and variant-wise annotation – automation methods follow in Section 2.5.

Feature-Wise Annotation (FW) is one of the simplest methods for performance modeling. It associates each (boolean) feature with a static performance attribute, and assumes that the performance attribute of the entire product is the sum of performance attributes of enabled features. The model can be created manually by a domain expert or automatically via machine learning. This section showcases the manual method by providing fictional hardware cost and binary size values for the example operating system product line. In a real-world use case, practitioners would obtain these using a combination of domain knowledge and benchmarks.

As the name suggests, hardware cost is dictated by the hardware architecture the product runs on, and is independent of Stack Guard and driver configuration. Thus, annotating each Arch sub-feature with the bulk price of the respective hardware platform (say,  $2 \in$  for AVR,  $4 \in$  for MSP430, and  $3 \in$  for ARM) is sufficient and the hardware cost model is complete.

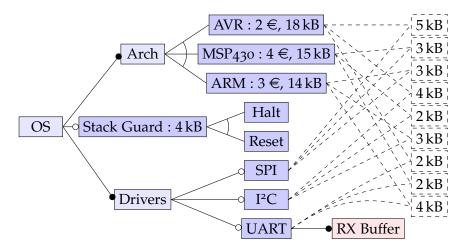

Figure 2.2: Feature model for a sample operating system product line, using feature- and variant-wise annotations to model hardware cost and kernel size.

We can start with the same approach for binary size. As each product is built for exactly one architecture, product line engineers can annotate each Arch sub-feature with the combined size of common and architecture-specific operating system components, excluding drivers and stack guard code: 18 kB for AVR, 15 kB for MSP430, 14 kB for ARM.

The stack guard feature is largely architecture-independent, and can also be annotated this way. When rounding to whole kilobytes, it increases binary size by 4 kB regardless of halt/reset configuration.

Drivers, on the other hand, work with architecture-specific peripheral interfaces. While the SPI driver introduces just 3 kB on MSP430 and ARM, it increases total size by 5 kB on AVR, so a simple annotation is not sufficient. This phenomenon is known as *feature interaction*, and it is becoming more and more common in today's increasingly complex software and ever-expanding feature models [Tër<sup>+</sup>22]. Prominent examples are cross-cutting concerns such as debug flags, optimization options, security features, and the hardware selection shown here.

Variant-wise annotations address this by considering interactions between related features [Sie+12b]. They can express performance attributes that are only relevant if two or more features are enabled. For instance, assuming that SPI takes up 3 kB on MSP430 and ARM, and 5 kB on AVR, a product line engineer will annotate the pairs (MSP430, SPI) and (ARM, SPI) with 3 kB, and (AVR, SPI) with 5 kB. They can do the same for I<sup>2</sup>C and UART. As the RX buffer is located in RAM, it does not affect binary size. Fig. 2.2 shows the resulting feature interaction model.

This combined variability and performance model allows for performance-aware configuration of the operating system product line. Anyone can predict the cost and size of arbitrary products within the product line by calculating the sum of all feature- and variant-wise annotations of enabled features, and also see how each feature affects them. For example, if a user is looking for an I<sup>2</sup>C-enabled kernel with minimal footprint, they immediately see that both MSP430 and ARM result in a 16 kB binary, whereas the AVR variant would take up 22 kB. The model also shows that ARM is cheaper than MSP430, so they may be inclined to use an ARM processor for this task.

While this works well in a toy example with just nine features and nine interactions, it turns into a significant engineering effort when applied to real-world product lines with hundreds to thousands of features and interactions. Machine learning offers an alternative approach for these cases: run benchmarks for different configurations and automatically generate a performance model using a suitable machine learning algorithm. Doing this at scale relies on the ability to extract configurations and feature vectors from variability models, run automated benchmark campaigns, and feed observations into model learning algorithms. This, in turn, benefits from machine-readable variability models and well-defined variability modeling languages.

#### 2.3 VARIABILITY MODELING LANGUAGES

From a language design point of view, the previous sections introduced variability models in a deliberately informal manner. Before moving on to textual models and actual variability modeling languages, let us take a step back and examine how these relate to the expressiveness and graphical representation of variability models.

Variability modeling languages (and domain-specific languages in general) distinguish between abstract syntax and concrete syntax [Don<sup>+</sup>84; BVo4]. Abstract syntax defines structure and expressiveness – in this case, feature hierarchies, feature types, and cardinalities. Concrete syntax defines the representation of language components – for instance the tree structure shown in Fig. 2.1.

A specific *variability modeling language* builds upon an abstract syntax that defines its features and expressiveness, e.g. whether it supports numeric features or complex cardinalities. In addition, it typically has at least one concrete syntax that defines the representation of feature models, for instance in a graphical or textual manner. Textual variability models are machine-readable by design. When created with appropriate tooling rather than printed in a document, graphical variability models are machine-readable as well and can be transformed into textual models or other representations, and vice versa.

Considering the relevance of machine-readability in this thesis, we will now examine existing variability modeling languages (also known as *feature modeling languages*) with a focus on their expressiveness and textual representation. In addition to expressiveness, the language choice also dictates the available options for performance prediction models, tooling support, and more [BSE19].

Variability modeling languages have been an active research subject for the past two decades [ES15]. Early approaches, such as the Feature Description Language, define text-based representations that build upon already-existing graphical representations [VK02]. They are limited to boolean features, relations, and constraints. While this allows for reasoning about any variability model by means of propositional calculus, the designers of the Feature Description Language already noted that numeric features and relations may be helpful extensions.

Forfamel and VSL, published only a few years later, support numeric feature attributes such as RX buffer size [AMSo6; Abe+10]. In fact, Forfamel handles arbitrary attribute types, including strings and numeric attributes with optional range limits. Its authors also suggest using a constraint language to express dependencies on feature attributes rather than just features. However, in the provided concepts and implementations, all attributes are purely informative. They can be configured by the user and read out by software, but cannot be reasoned upon. For example, they cannot express the RX Buffer  $\leq 256 \land (\text{AVR} \Rightarrow \text{RX Buffer} \leq 64)$  constraint from Section

Still, this provides an early method for augmenting features with performance attributes. By specifying constant feature attributes such as hardware cost or binary size, and assuming that the cost or size of a product is the sum of the cost or size of all selected features, practitioners and algorithms can predict overall product cost or size. This is a hack, though: feature attributes were not meant for this task, and there are neither syntax nor semantic rules that properly define the aggregation of non-functional properties.

TVL and VELVET introduce just this: aggregate functions for feature attributes [Bou<sup>+</sup>10; Ros<sup>+</sup>11; Sie<sup>+</sup>11]. For instance, the following TVL expression declares that a parent feature's text segment size is the sum of the text segment size of all enabled child features:

```

int textSize is sum(selectedChildren.textSize);

```

Thus, practitioners can define product performance based on non-functional properties, and reason about optimal configurations. However, they can only do so for performance properties that are a simple aggregation of feature-specific values – i.e., the contribution of each feature is independent of the configuration of other features. As we have already seen, this is not always the case.

Hence, modern variability modeling approaches like Clafer/Clafer-Moo and SPL Conqueror include methods to specify feature interaction [BCW10; Bąk+16; Ant+13; Sie+12b; Sie+12a]. For example, in Clafer, engineers may specify that enabling the Debug feature increases total binary size by 10% on average:

```

binarySize = (sum Feature.binarySize) * (Debug ? 1.1 : 1)

```

Listing 2.1: UVL feature model for a sample operating system product line.

```

features

0S {abstract}

mandatory

Arch {abstract}

alternative

AVR

MSP430

ARM

Drivers {abstract}

optional

I2C

UART

optional

StackGuard

alternative

Halt

Reset

constraints

StackGuard => MSP430 | ARM

```

One of the most recent variability modeling language specimen is the Universal Variability Modeling Language (UVL). It is part of an initiative that aims to find a community consensus on best practices for variability modeling, and to define a corresponding universal variability modeling language [Sun<sup>+</sup>21b]. In this spirit, there is support for interactive generation and usage of UVL models [Sun<sup>+</sup>21a], and for conversion to and from other variability modeling languages [Rom<sup>+</sup>22].

As part of this initiative, practitioners expressed their priorities for variability modeling language features in questionnaires. For example, seven of 20 participants indicated that feature attributes are nice to have, and two deemed them as absolute necessities [Sun<sup>+</sup>21b].

As of late 2022, a first formal definition of UVL exists, and the authors state that it may be refined in the future. This UVL version does not support feature attributes by itself, but there is an experimental superset of UVL with feature attribute support. So, even after two decades of research, choosing a suitable variability modeling language is far from trivial.

After this brief history lesson, let us examine how two recent textual variability modeling languages express the OS feature model defined in Fig. 2.2. Listing 2.1 contains a UVL model for this operating system product line example. Its nested definitions closely resemble the tree structure of Fig. 2.1. As UVL does not (yet) support numeric features, the model does not contain RX buffer size and the associated constraint.

Listing 2.2 shows a Clafer model for the same product line, including performance attributes using feature- and variant-wise annotations.

Listing 2.2: Clafer feature model for a sample operating system product line, annotated with cost and size attributes.

```

abstract Feature

cost : integer

size : integer

abstract OS

xor Arch

AVR : Feature [ (cost = 2), (size = 18) ]

MSP430 : Feature [ (cost = 4), (size = 15) ]

ARM : Feature [ (cost = 3), (size = 14) ]

Drivers

SPI : Feature ? [ size = AVR ? 5 : 3 ]

I2C : Feature ?

[ size = AVR ? 4 : MSP430 ? 2 : 3 ]

UART : Feature ? [ size = ARM ? 4 : 2 ]

RXBuffer : integer

xor StackGuard : Feature ? [ size = 4 ]

Halt : Feature

Reset : Feature

total_cost : integer [ total_cost = sum Feature.cost ]

total_size : integer [ total_size = sum Feature.size ]

[ StackGuard => MSP430 || ARM ]

[ UART => RXBuffer <= 256 ]

[ UART && AVR => RXBuffer <= 64 ]

```

Here, too, there is a clear relation between textual variability model and tree structure. However, due to language-level support for abstract features, inheritance, and performance attributes, the textual representation is harder to digest.

My own research focuses on working with existing real-world product lines, or configurable software projects that behave similar to product lines. In general, these do not come with a feature model defined in UVL, Clafer, or a similar formal variability modeling language. Instead, they either do not have a formal variability model at all, or rely on the Kconfig variability modeling language. Hence, although the methods I will present in this thesis are applicable to any of the aforementioned variability modeling languages, the implementation builds upon Kconfig-based product lines and software projects.

### 2.4 THE KCONFIG LANGUAGE

Kconfig is far from an ideal variability modeling language. It is meant to solve the practical issue of Linux kernel configuration and has not been developed according to software engineering research principles [EKS15]. However, its wide-spread adoption in open-source software projects such as Linux or busybox makes it a suitable vari-

ability modeling language for evaluation of real-world applications. More so, even if projects like Linux are not developed according to the guidelines of *Software Product Line Engineering* (SPLE), they can be understood as software product lines [Sin<sup>+</sup>o<sub>7</sub>]. Thus, building on top of Kconfig ensures compatibility with several ready-to-evaluate software projects. Using those as evaluation targets also helps ensure that the results presented in this thesis apply to real-world product lines.

The Kconfig ecosystem uses a Kconfig text file to define feature models. In contrast to UVL and other languages from the SPL community, a Kconfig model does not define a feature tree via nesting or references. While the choice and menu keywords allow engineers to define a group of features with a common parent, these are not mandatory. Instead, Kconfig configuration frontends infer a tree structure from feature dependencies as well as choice and menu groups. So, the tree structure is only present at configuration time, and only when using a suitable Kconfig frontend.

A Kconfig file is made up of config entries that define individual features. Each feature is either bool (yes / no, a boolean feature), tristate (yes / module / no, often used to decide whether features should be compiled into the kernel, into separate module files, or not at all), int / hex (numeric), or string (e.g. the path to the build toolchain). Features have a user-visible prompt and optional help text. Additionally, they can depend on boolean expressions that reference other features (depends on), reverse-depend on features (select/imply), have default values, and be limited to a numeric range.

Entries without a prompt are legal, but invisible in all configuration frontends and thus do not express features. Combined with reverse dependencies of (visible) features, these express common traits of individual features and can help reduce clutter in conditional source code blocks.

menu and choice entries define parts of the menu tree that users see when using a Kconfig frontend for configuration. A menu is an abstract group of related features, such as the Drivers node in the operating system example (Fig. 2.1). A choice offers an alternative between several child features in an exclusive-or relation. By default, it is abstract (and, thus, mandatory); when declared as optional it becomes a concrete feature that can be enabled and disabled.

Kconfig frontends such as kconfig-qconf or kconfiglib² store the user-provided configuration in a .config file. Each line corresponds to a single config entry; however, the .config file only provides values for entries whose dependencies are satisfied. Each user-configurable feature (and invisible entry) with satisfied dependencies has an associated value in the .config file, and features (and entries) whose

<sup>2</sup> https://github.com/ulfalizer/Kconfiglib

dependencies are not met do not. Thus, even if Kconfig has not been designed with product line engineering in mind, extraction of feature vectors from .config files is viable.

Listing 2.3 shows a Kconfig definition of the feature model defined in Fig. 2.1. For details, please refer to the language specification<sup>3</sup>. Note that, just like UVL, Kconfig does not support performance attributes.

#### 2.5 MACHINE LEARNING

As stated earlier, rather than relying on manual annotation by a domain expert, developers can also employ machine learning algorithms for automatic generation of performance models, or use a combination of machine learning and domain knowledge.

Of course, machine learning algorithms do not come up with performance models out of thin air. In order to be usable for this task, they must have access to training data consisting of product line configurations (feature vectors)  $X = \{\vec{x}_1, \ldots, \vec{x}_m\}$  and performance attributes (e.g. binary size or processing throughput)  $Y = \{y_1, \ldots, y_m\}$ . Each pair  $(\vec{x}_j, y_j)$  describes a configuration (benchmark input)  $\vec{x}_j \in \mathbb{R}^n$  and the corresponding performance attribute (benchmark output)  $y_j \in \mathbb{R}$ . In cases where the index in the sets X and Y is not relevant,  $(\vec{x}, y)$  refers to any pair of matching benchmark data. The variable  $x_i$  refers to the i-th feature vector element (the i-th configurable feature), regardless of its concrete value.

From X and Y, machine learning algorithms infer a model function  $f: \vec{x} \to y$  that ideally behaves just like the manually specified performance prediction models examined earlier. Some algorithms require a user to provide the model structure (e.g. a function template or a neural network layout); others are capable of generating it by themselves and only require training data as input. In both cases, users may be able to configure training *hyper-parameters* that affect e.g. trade-offs between model accuracy and model complexity.

Machine learning is a popular research field, with applications as diverse as anomaly detection in time series, identification of people in images, or generating media from text prompts. My own work only touches a small part of that, namely learning to predict individual numeric performance attributes from numeric (and, in Chapter 7, categorical) feature vectors. While anomaly detection and computer vision will come into play later, they are not relevant for performance model generation, and therefore not within the scope of this chapter.

Note that I only consider machine learning methods and models that predict a single performance attribute. By combining several models (e.g. one for hardware cost and one for binary size), users can still obtain integrated performance models that predict multiple attributes, such as the one shown in Fig. 2.2. I will also leave out

<sup>3</sup> https://kernel.org/doc/html/latest/kbuild/kconfig-language.html

Listing 2.3: Kconfig model for a sample operating system product line.

```

choice arch

bool "Architecture"

config avr

bool "AVR"

config msp430

bool "MSP430"

config arm

bool "ARM"

endchoice

choice stack_guard

bool "Stack Guard"

optional

depends on msp430 || arm

config guard_halt

bool "Halt System on Stack Overflow"

config guard_reset

bool "Reset System on Stack Overflow"

endchoice

menu "Drivers"

config spi

bool "SPI"

config i2c

bool "I2C"

config uart

bool "UART"

config uart_rx_buf

int "RX Buffer"

default 32

range 0 256

range 0 64 if avr

depends on uart

```

endmenu

string features – in my experience, these generally refer to attributes that do not influence system performance, such as compiler paths or component identifiers. Hence,  $\vec{x} \in \mathbb{R}^n$  holds for all feature vectors in this chapter.

With these criteria in mind, two kinds of machine learning algorithms are especially interesting: least-squares regression and regression trees. Both predict a single output variable from numeric input variables and use model structures with limited complexity. Also, both have been used for SPL performance prediction in the past. Least-squares regression is closely related to feature- and variant-wise annotations; it relies on a fixed, user-provided model structure. Regression tree learning algorithms build the model structure from training data and expose hyper-parameters to limit its complexity.

As it relies on user-provided model templates, least-squares regression alone is not a suitable solution for RQ3 ("... without requiring manually provided domain information or model structure"). It is, however, useful as an evaluation target, and – as we will see in the next chapter – it is also possible to extend least-squares regression so that it learns the structure by itself.

The remainder of this section covers both learning algorithms in detail. It also presents a lookup table model that is not useful for performance prediction of configurations that were not present in training data, but will prove helpful when it comes to putting the complexity and accuracy of least-squares regression, regression forests, and other models into perspective.

## 2.5.1 Least-Squares Regression

Broadly speaking, regression analysis is a machine learning method that adjusts (*fits*) weights  $\vec{\beta}$  in a function template  $f(\vec{x})$  so that  $f(\vec{x}) \approx y$  for training data pairs  $(\vec{x}, y)$  [DS98]. It does not build the function template itself, but relies on users or pre-processing algorithms to provide it.

Regression analysis algorithms achieve this by minimizing the *loss* of the error term  $\varepsilon = y - f(\vec{x})$ . Loss represents prediction uncertainty and thus model error. In least-squares regression, it is the eponymous *Sum of Squared Residuals* (SSR)  $\sum_i \varepsilon_i^2$ .

$$SSR(f, X, Y) = \sum_{i=1}^{m} (y_i - f(\vec{x}_i))^2$$

(2.1)

The method for adjusting  $\vec{\beta}$  in the learning process depends on the regression algorithm in question and the function template. These also decide whether the loss of the fitted output function really is a global minimum in the  $|\vec{\beta}|$ -dimensional plane of functions  $f(\vec{x})$ . If it is a global minimum, the resulting weights  $\vec{\beta}$  are guaranteed to

give optimal predictions with the provided function template on the available training data. Otherwise, there might be a different set of weights  $\vec{\beta}$  that gives a better fit with lower model error.

## Algorithms

The function template  $f(\vec{x}) = \beta_0 + \sum_{i=1}^n \beta_i x_i$  is a special case that is also known as *Linear Regression*. Here, the function f and the loss function SSR are differentiable. By setting the partial derivatives of SSR to zero and solving for  $\vec{\beta}$ , anyone – including computer algorithms – can find weights that correspond to a global minimum of the loss SSR. Hence, in linear regression, the resulting weights  $\vec{\beta}$  are guaranteed to provide an optimal fit on the provided training data.

Some non-linear function templates can be handled in the same manner. When working with arbitrary function templates, though, f and SSR may not be differentiable – or solving for  $\vec{\beta}$  is not feasible due to an insufficient amount of available computing resources. In this case, a common approach is approximating  $\vec{\beta}$  via gradient descent.

In a nutshell, given some values for  $\vec{\beta}$ , this method computes its gradient on SSR(f,X,Y) – so, the direction of change that corresponds to the steepest increase of model loss. Adjusting  $\vec{\beta}$  in the inverse direction decreases it and thus reduces loss. Afterwards, a gradient descent algorithm computes a new gradient using the updated  $\vec{\beta}$  values, and continues until the algorithm converges (i.e., the loss reduction from adjusting  $\vec{\beta}$  is below a user-defined threshold) or another stop criterion (e.g. maximum number of iterations, or change in  $\vec{\beta}$  between consecutive iterations below threshold) has been reached.

While this works with arbitrary functions, it has limitations that users must be aware of. Most prominently, as gradient descent approximates the differential of the loss function and adjusts  $\vec{\beta}$  in steps rather than working with a continuous and differentiable function, there is a risk of not converging within a limited time or ending up in a local rather than a global minimum of the loss function. It also requires users to declare initial values for  $\vec{\beta}$ , and may be non-deterministic e.g. if the initial  $\vec{\beta}$  is random. In this thesis, the algorithm always starts with  $\vec{\beta} = \vec{1}$ .

Nevertheless, when users are aware of these limitations, least-squares regression can be a powerful machine learning algorithm. It has been used successfully for numerous tasks in the past, including performance models for software product lines with a custom pre-processing algorithm for function template generation [Sie<sup>+</sup>15].

Finally, *Symbolic Regression* is an extension that is capable of coming up with function templates on its own. It uses genetic algorithms to combine function snippets into a function template that balances prediction accuracy and function complexity. This enables it to, for instance, determine basic natural laws from empiric observations [SLo9]. However, it is prone to overfitting: it tends to learn training data by

| BENCHMARK #              | 1  | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9  | 10 | 11 | 12 |

|--------------------------|----|----|----|----|----|----|----|----|----|----|----|----|

| $x_1$ (AVR)              | 1  |    |    | 1  | 1  | 1  |    |    |    |    |    |    |

| $x_2$ (MSP430)           |    | 1  |    |    |    |    | 1  | 1  | 1  |    |    |    |

| $x_3$ (ARM)              |    |    | 1  |    |    |    |    |    |    | 1  | 1  | 1  |

| $x_4$ (Halt)             |    |    |    |    |    |    |    |    |    |    |    |    |

| $x_5$ (Reset)            |    |    |    |    |    |    |    |    |    |    |    |    |

| $x_6$ (SPI)              |    |    |    | 1  |    |    | 1  |    |    | 1  |    |    |

| $x_7$ (I <sup>2</sup> C) |    |    |    |    | 1  |    |    | 1  |    |    | 1  |    |

| $x_8$ (UART)             |    |    |    |    |    | 1  |    |    | 1  |    |    | 1  |

| y (Size [kB])            | 18 | 15 | 14 | 23 | 22 | 20 | 18 | 17 | 17 | 17 | 17 | 18 |

Table 2.1: Excerpt of configurations and corresponding kernel sizes for a sample operating system product line. Each row describes a configuration variable  $x_i$  or performance attribute y. Empty cells indicate disabled features (0). Configurations 13 through 24 (not shown) correspond to 1 through 12 with Halt enabled and a size of y+4. Configurations 25 through 36 (not shown) correspond to 1 through 12 with Reset enabled and a size of y+4.

heart rather than expressing the underlying behaviour [Ray<sup>+</sup>19]. This can already happen in low-dimensional configuration spaces and is exacerbated by noisy data [FBS18]. Considering these limitations, and that I am not aware of researchers applying symbolic regression to performance model generation, I will not go into further detail here.

## Example

Assume that we have benchmarked our sample operating system product line and obtained the results shown in Table 2.1. Note that this is a deliberately simplified benchmark example that is only meant to illustrate the relation between least-squares regression, performance models, and feature- and variant-wise annotation. The benchmark results are not suitable in practice, as they do not contain configurations where more than one driver is enabled. Thus, learning algorithms cannot determine whether driver features interact with each other e.g. due to shared code.

As noted earlier, the function template must be provided by the user or a pre-processing algorithm. In this case, we use a simple pre-processing algorithm which assumes that each boolean feature contributes to the modeled performance attribute, and that there are no constant components and no feature interaction. So, given eight boolean features  $x_1$  to  $x_8$ , the function template is  $f(\vec{x}) = \sum_{i=1}^8 \beta_i x_i$ .

After fitting, e.g. using Python3's scipy.optimize.least\_squares, and rounding  $\vec{\beta}$  to kilobytes, the result is  $\vec{\beta} = (18, 14, 14, 4, 4, 4, 3, 3)$ . When transformed to feature-wise annotations, this means that AVR, MSP430 and ARM result in a base kernel size of 18, 14, and 14 kB, respectively. Halt and Reset contribute 4 kB each, and the SPI, I²C and UART features contribute 4, 3, and 3 kB.

This does not align with the observations shown in Table 2.1. Common reasons for this kind of model error are noisy data and unsuitable function templates. In this case, it is the latter: as we have already seen in Fig. 2.2, there are feature interactions between architecture selection and driver code, so a pure feature-wise annotation template is insufficient.

So, let us assume that a more sophisticated pre-processing algorithm has identified feature interactions in the product line, and generated the function template  $f(\vec{x}) = \sum_{i=1}^5 \beta_i x_i + \sum_{i=1}^3 \sum_{j=6}^8 \beta_{i,j} x_i x_j$ . Now,  $\beta_i$  corresponds to feature-wise attributes, and  $\beta_{i,j}$  to the interaction between features  $x_i$  and  $x_j$ . After fitting this function,  $\vec{\beta}$  is nearly identical to the model shown in Fig. 2.2. The only difference is that  $\vec{\beta}$  annotates Halt and Reset with 4 kB each instead of the parent Stack Guard feature – which is not surprising, as Table 2.1 does not contain a feature vector component for Stack Guard.

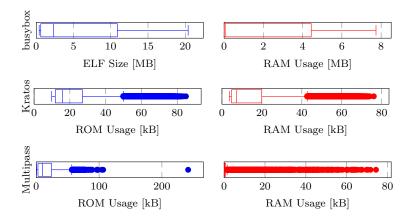

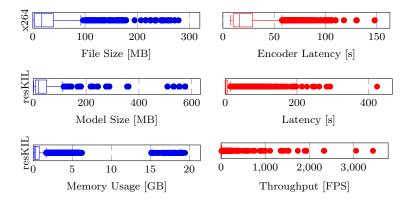

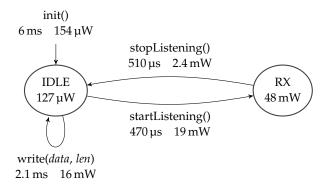

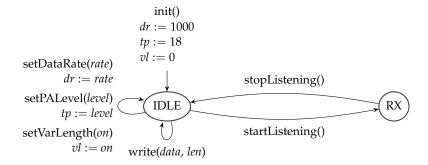

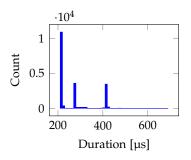

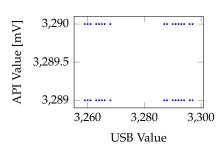

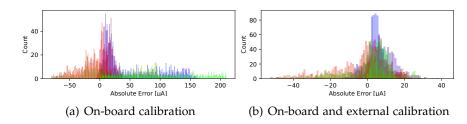

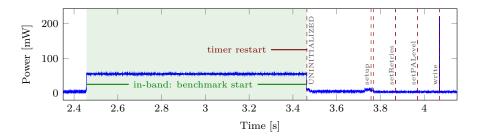

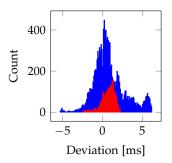

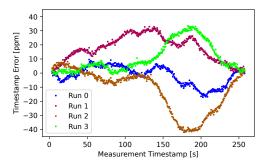

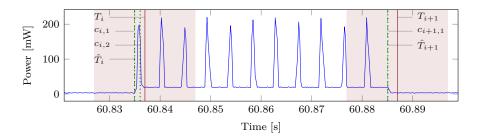

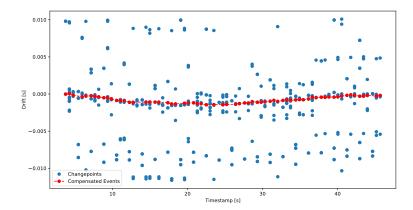

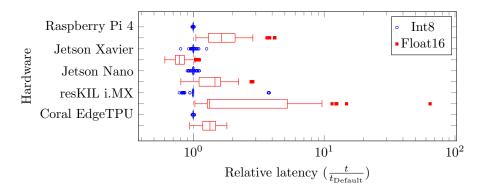

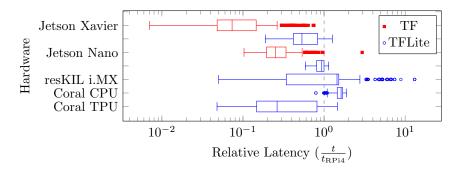

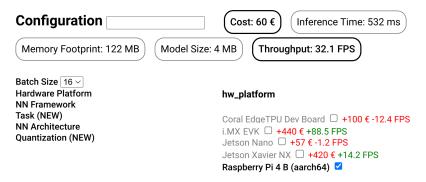

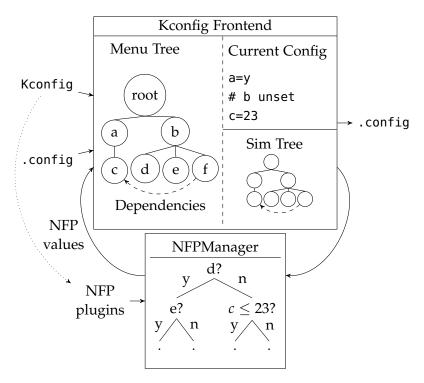

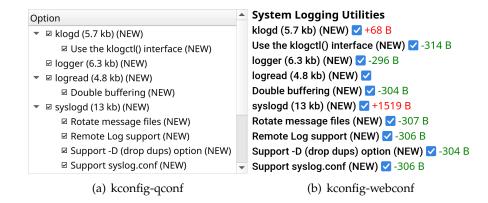

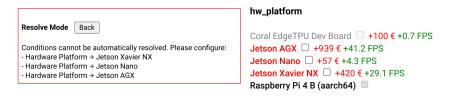

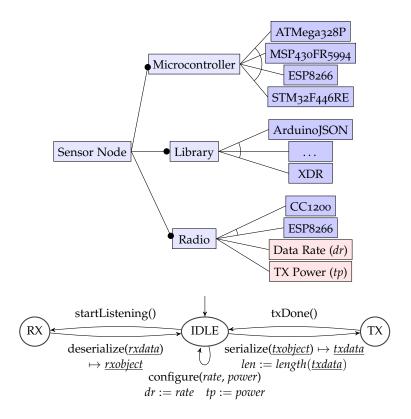

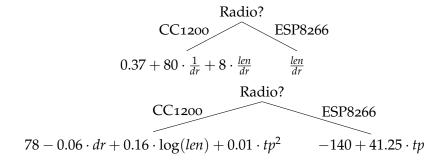

#### Limitations